# Adaptive Equalization for Interchip communication

Dénis Gaspar Nogueira da Silva

FOR JURY EVALUATION

Mestrado Integrado em Engenharia Eletrotécnica e de Computadores

Supervisor at FEUP: Prof.Henrique Salgado

Supervisor at Synopsys: Engineer Luís Moreira

Supervisor at Synopsys: Engineer Sérgio Silva

June 30, 2014

### Resumo

A area da eletrónica é uma industria em constante evolução e é a fundação de novas tecnologias em outras áreas como a indústria automóvel medicina e muitas outras.

As empresas de projecto e fabrico de circuitos integrados constituem a base da evolução tecnológica fornecendo tecnologias que possam ser integradas por outras empresas em sistemas mais complexos para o desenvolvimento de um determinado produto para o consumidor.

A Synopsys é uma empresa que se dedica, além de outros temas, ao design de interfaces de altas velocidades para barramentos de comunicações digitais, fornecendo circuitos integrados para protocolos como USB, HDMI, MIPI, SATA e outros.

Actualmente a velocidade de transmissão das interfaces desenvolvidas pela Synopsys atingem a ordem dos Gbs por link, a transmissão a essas velocidades não seria possivel sem sistemas que compensem a distorção causada pelos canais utilizados na comunicação.

A distorção é causada pelo facto dos canais possuirem uma resposta em frequência cuja atenuação é dependente da frequência,o que causa que os bits transmitidos nesse canal aumentem a largura original do seu impulso e interferindo com os bits adjancentes, efeito que é conhecido como Interferência Inter-Simbólica.

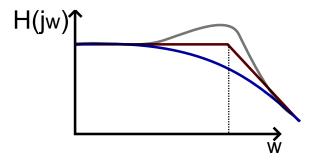

A eliminação da interferência intersimbólica é conseguida através de circuitos de igualização que realizam respostas em frequência inversas à do canal para tornar a resposta em frequência total o mais plana possível.

No entanto por vezes é necessário realizar igualização sem que se saiba ao certo qual a distorção introduzida, de facto a distorção pode até mesmo mudar durante a operação da interface o que leva que a igualização se torne adaptativa.

Este assunto tem sido uma área muito estudada nos ultimos anos devido á necessidade das interfaces de comunicação de realizarem comunicações com débitos cada vez mais elevados, o que leva que a questão da eliminação da interferencia inter simbólica se torne cada vez mais importante.

O objectivo desta tese é estudar e testar métodos de adaptar os filtros de igualização presentes numa interface de alta velocidade desenvolvida pela Synopsys.

O estudo terá em conta as limitações introduzidas pelos débitos utilizados, Características dos canais e pelas restrições de complexidade impostas aos sistemas de adaptação.

### **Abstract**

The area of electronics is in constant evolution and is the foundation of new technological breakthroughs in areas like the automobile industry, medicine and many others.

Companies dedicated to the design and manufacturing of integrated circuits are the basis of the technological advance by providing technology that can be integrated by other companies in more complex systems in the development of products for the final consumer. Synopsys is a company dedicated to the design of high speed serial interfaces to digital buses, providing integrated circuits that support protocols as USB, HDMI, MIPI, SATA and others.

Nowadays the interfaces developed by Synopsys operate at bit rates in the order of the Gbs per link, the transmission at that bit Rates would not be possible without systems that compensate the distortion caused by the channels used in the communication.

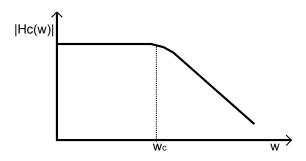

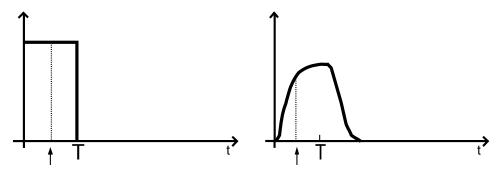

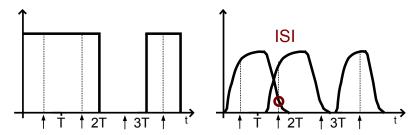

The distortion is caused by the fact that the channels have a frequency response with frequency dependent losses, this causes the spreading of the transmitted pulses to the adjacent bits causing Inter Symbol Interference.

The elimination of Inter Symbol Interference is achieved through equalizing circuits that compensate the channel by introducing a frequency response that is the inverse of the one of the channel, to make the overall frequency response as flat as possible.

Sometimes there is the need to design equalizing circuits without the knowledge of the amount of distortion that is introduced by the channel. In fact, the channel characteristics may even change during the operation of the interface leading to Adaptive equalization.

The field of adaptive equalization has been a very hot topic in research the last couple of years due to the increase in the speeds used in the communication interfaces,henceforth the topic of the elimination of Inter Symbol Interference gained relevance.

The objective of this thesis is to study and test methods that perform adaptation of the equalizing filters present in a high speed interface designed by Synopsys.

The study will take into account the limitations introduced by the bit Rates used in the interface, the characteristics of the channels and complexity restrictions imposed to the adaptation system.

### Acknowledgements

I would like to express my gratitude to:

My family who always supported me through all my five years of college, i am sure that without them i would not be the person I am today. So here is a big thanks to all my five brothers Maria, Julio, Ricardo, Cláudia and Romeu, and my parents Maria and José, who sacrificed a lot to get me to finish my degree.

To all my friends who from time to time would make me shift my mind from this thesis and have some fun.

To Pedro Araújo for supporting me and dealing with my moments of insanity.

To all the people in Synopsys, specially Henrique Martins, Hélder Campos and my friends in the analogue team: Bruno, Patrício, Hugo and Nuno that always provided me with the best cookies.

To Bárbara for being my biggest supporter during this six months that I worked on my thesis.

To Célio Albuquerque for giving me the opportunity of developing my dissertation in such a great environment that is Synopsys.

To my supervisors at Synopsys, Sérgio Silva and Luís Moreira for opening a few moments on their busy schedule, to share some of their knowledge and experience. I would also would like to say that without their guidelines and advice I wouldn't have been able to finish my thesis.

To my supervisor at FEUP, Henrique Salgado for all suggestions, discussions and editing assistance during the development of this dissertation.

Finally, to FEUP for giving me the best years of my life.

Dénis Silva

### **Contents**

| 1 | Intr | oduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 1  |

|---|------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----|

|   | 1.1  | Motivation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 2  |

|   | 1.2  | Goals                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          | 2  |

|   | 1.3  | Structure of the document                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 3  |

| 2 | Digi | tal communication systems                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5  |

|   | 2.1  | Inter-Symbol Interference                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      | 5  |

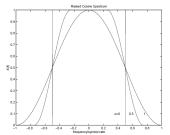

|   |      | 2.1.1 Nyquist condition                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 7  |

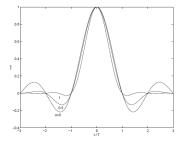

|   |      | 2.1.2 Jitter                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 9  |

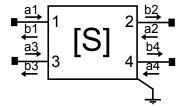

|   |      | 2.1.3 Scattering Parameters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | C  |

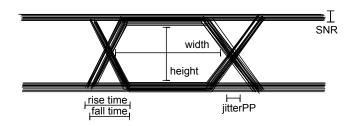

|   |      | 2.1.4 Eye Diagram                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 1  |

|   | 2.2  | Strategies to fight ISI                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2  |

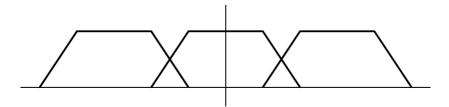

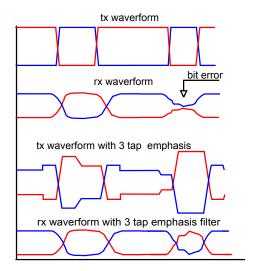

|   |      | 2.2.1 Fight ISI with bit shaping                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 2  |

|   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 3  |

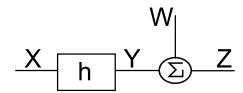

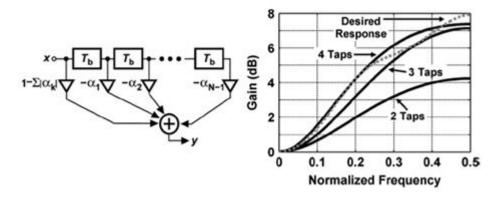

|   |      | 2.2.3 Equalization with Filters                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 5  |

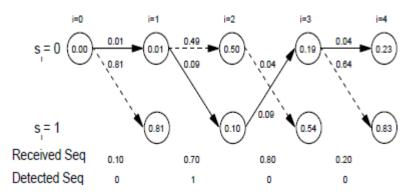

|   |      |                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 9  |

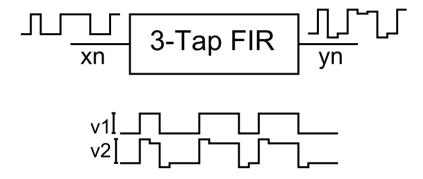

|   |      | 2.2.5 Discrete Time Equalizers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | :2 |

|   | 2.3  | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 2  |

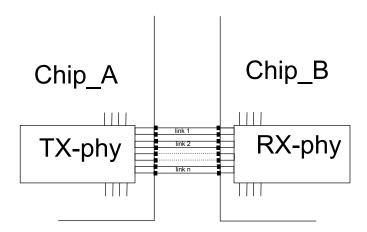

| 3 | Syst | em Specification 3                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 3  |

|   | 3.1  | The Phy                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 4  |

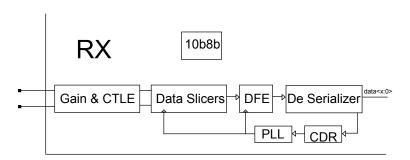

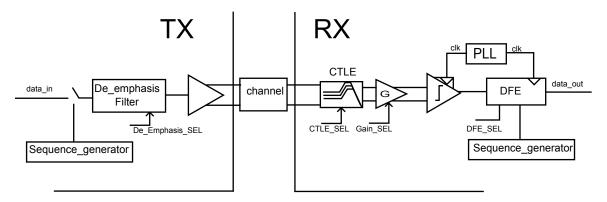

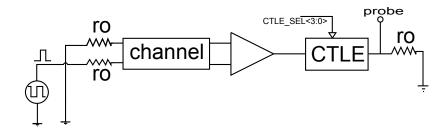

|   |      | 3.1.1 Architecture of the PHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 4  |

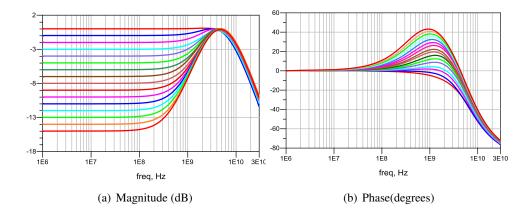

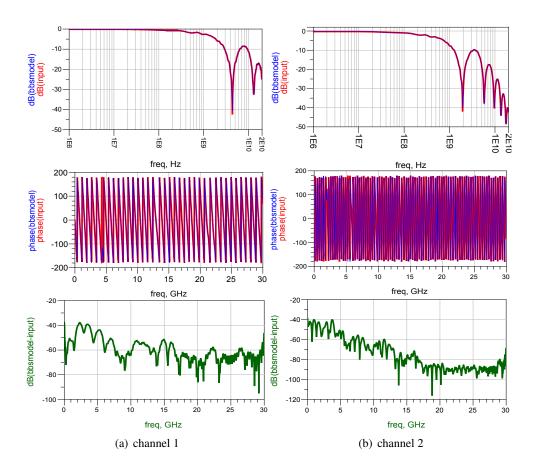

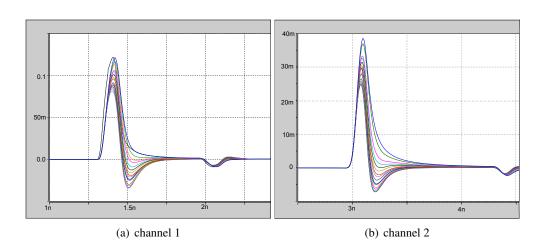

|   |      | 3.1.2 Characterization of the PHY                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 5  |

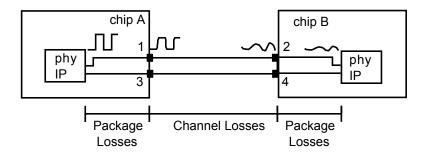

|   | 3.2  | The transmission environment                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   | 7  |

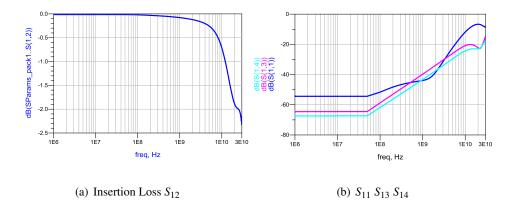

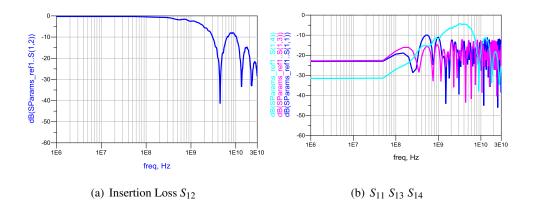

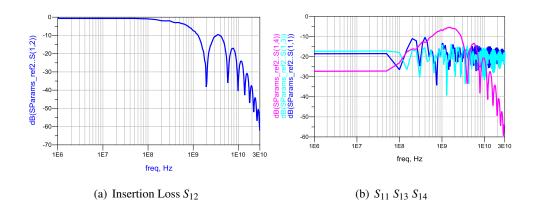

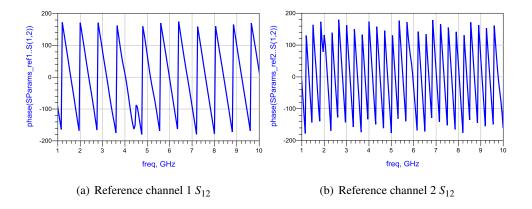

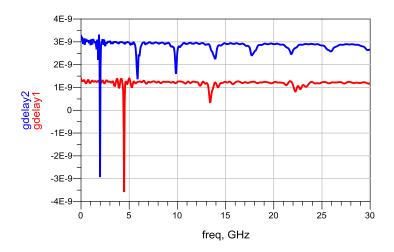

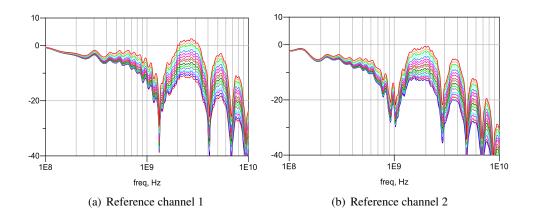

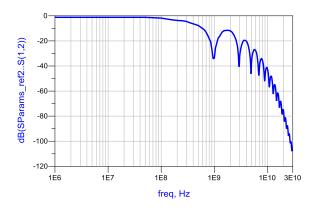

|   |      | 3.2.1 Transmission environment S-Parameters Simulation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         |    |

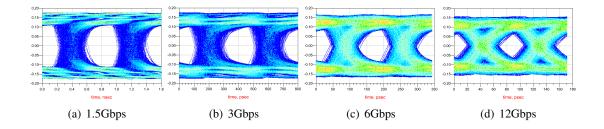

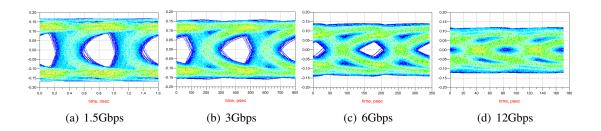

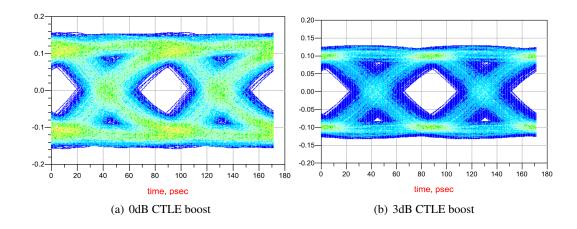

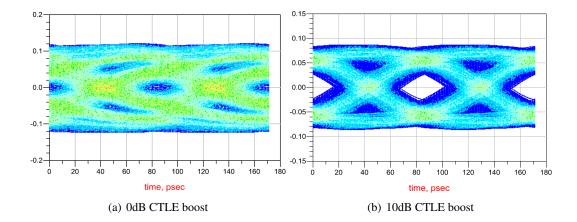

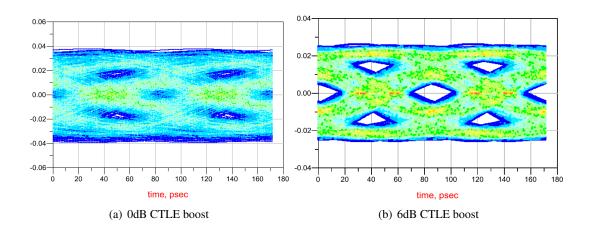

|   |      | 3.2.2 Eye diagrams for the different bit Rates                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |    |

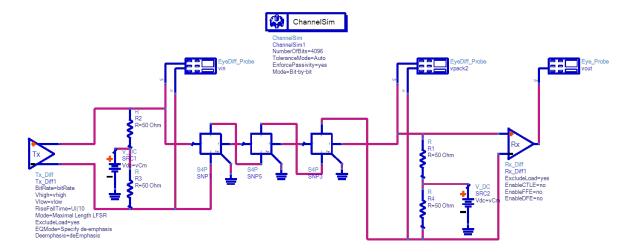

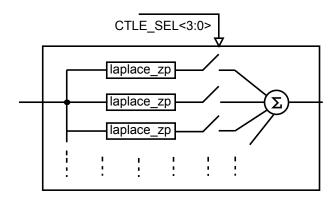

|   | 3.3  | Proposed equalization structure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |

|   | 3.4  | Summary                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        |    |

| 4 | Fan  | alization architecture 4                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                       | 15 |

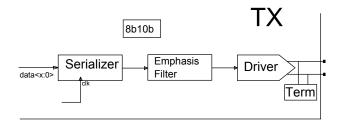

| - | 4.1  | De-Emphasis Study                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

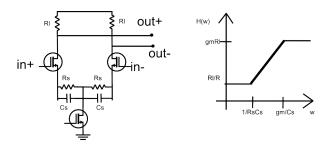

|   | 4.2  | CTLE design                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |    |

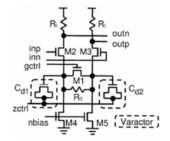

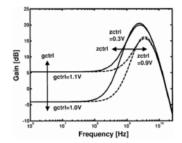

|   | 4.2  | 4.2.1 CTLE adaptation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |    |

|   |      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

|   | 12   | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

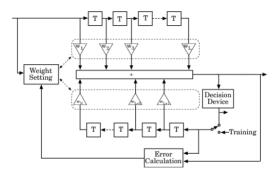

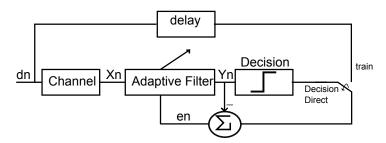

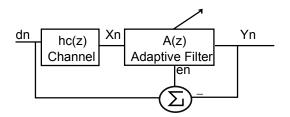

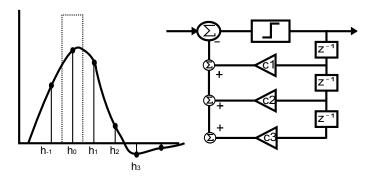

|   | 4.3  | , and the second |    |

|   |      | 1                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              |    |

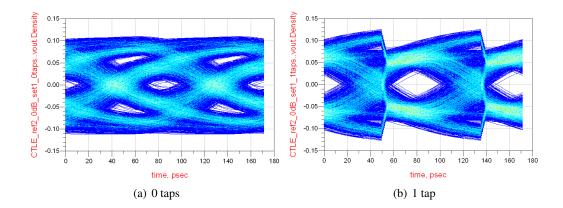

|   | 4 4  | 4.3.2 DFE simulations in Hspice                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |    |