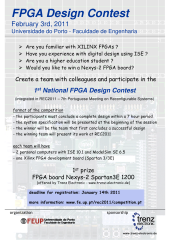

FPGA Design Contest

An FPGA design contest for groups of undergraduate students will take place on the first day of REC 2011.

The participating groups will receive the specification of the design at the start of the contest, and they will have the rest of the day to design and implement the corresponding system.

All groups will use the same resources (provided by the organization):

- a personal computer with Xilinx ISE (10.1 or 11.1) and Modelsim 6 simulator;

- a board with a Xilinx Spartan 3/3E FPGA.

The winner will be the first group to present a complete implementation of the system. The winning group will make a presentation of their work on the following day, just before the closing session of REC 2011.

PT

PT