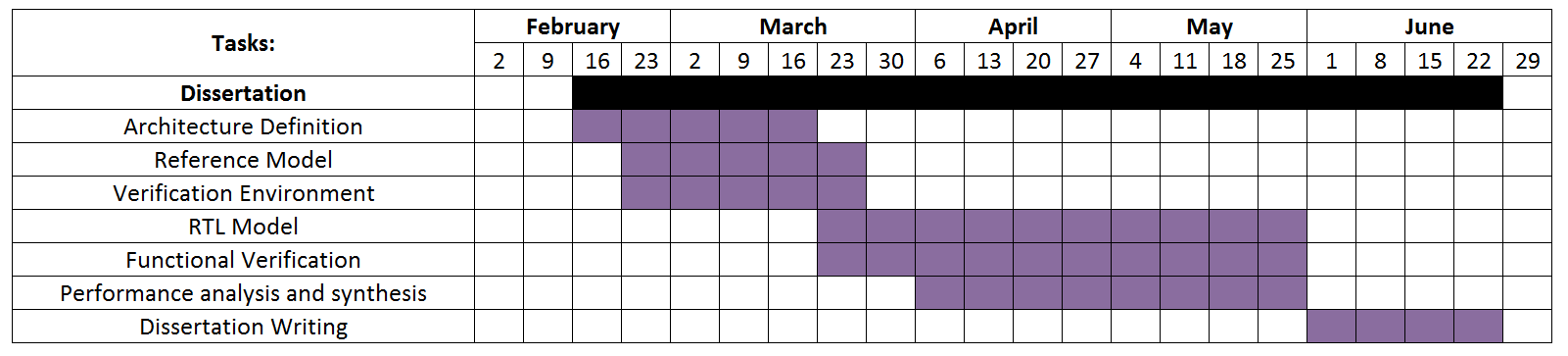

The development of this thesis consists in a series of different tasks that can be performed sequentially or with a certain degree of parallelism. A proposed planning for the scheduling of this tasks is presented in the figure.

During the first task, Architecture Definition, the architecture and the verification environment will be developed with a higher level of detail upon the basis developed in the Preparation for the Dissertation course in the first semester. In this phase the quantization of coefficients and operands for all mathematical operations will be defined and the filters for chroma resampling and the hardware implementation of the gamma functions will be designed. This tasks will be performed with Matlab and the reference model to be developed in C and the design decisions will be based on the comparison of the results offered by the different approaches.

A reference model of the system will be developed in C for utilization as golden model during verification tasks with the verification environment. The verification plan will be detailed during the Verification Environment development phase.

The reference model will be translated into a synthesizable Verilog version which will be functionally tested while it is being developed. The synthesis of the system will be done as soon as possible to provide performance analyses upon which the system can be further developed and upgraded. The main strategy here is to start by a straightforward implementation of the module and then develop upon it to have a basis for comparison of different design strategies.

Finally, the last weeks will be dedicated to the writing of the Dissertation.