Posted on January 4th, 2011 by Lu�s Cruz

Posted on Jun 21st, 2011 by Lu�s Cruz

- Thesis writing Done

- Web Page Updated to include Thesis Report

Posted on Jun 21st, 2011 by Lu�s Cruz

- Thesis writing ongoing

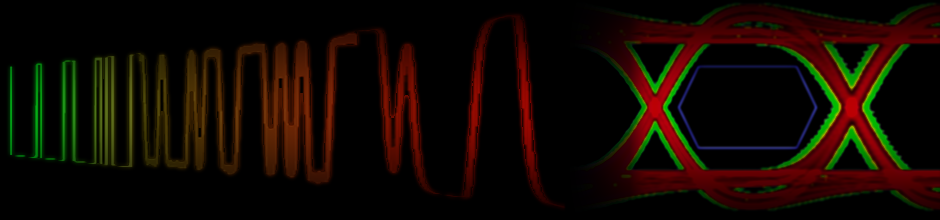

- Simulations performed to extract waveforms for thesis document

Posted on Jun 5nd, 2011 by Lu�s Cruz

- Software obtained results were cross-checked with lab ones

- Software support diagrams were created

- Thesis document creation is now the priority

- On going

Posted on May 22nd, 2011 by Lu�s Cruz

- Signal analysis classes created

- Eye diagram generation class created

- Analog parameters extraction class created

- Channel/Equalizer frequency response class created

- Added Signal analysis report creation inside signal analysis classes

- Added Data generation with possibility to add jitter

- Added support for data generation with pre-emphasis

- Created top level script to generate reports from raw data stored on .csv files

- The intent is to characterize interfaces where clock and data are transmitted from

TX macro to RX macro

- The frequency relation between data clock and line clock is equal to 10

- Created class to perform the convolution between analog signals and frequency responses

- Created top level script for channel characterization

- Clock Recovery Unit

- Cable Modeling

- Equalizer Modeling

- Jitter Modeling

- Data Pattern Generation

- Jitter Analysis

- Eye diagram creation

- Analog parameters extraction

- Added support statistical eye diagram generation

Posted on May 1st, 2011 by Lu�s Cruz

- Python Classes creation to analyze analog signals (crossing point and period extraction)

- Python Class creation to over sample analog signals

- Python Class creation to under sample analog signals

- Python Class creation to perform Clock Recovery from analog signals

- Included jitter addition tasks on analog signals processing Python Classes

- Python Class to perform cable equalization

- On going

- Python Class creation to perform the convolution between analog

signal and reference equalizer

- Python Class creation to perform Eye diagram measurements

- Necessary to improve the algorithm responsible for the frequency extrapolation

Posted on April 19th, 2011 by Lu�s Cruz

- Python Class creation to include the frequency to time domain functions

- Impulse Response generation from band limited S-parameters

- Impulse Response generation from a defined H(jw) function

- Spice cable simulation to extract S-parameters

- Spice impulse response generation for pre-defined LOW-PASS circuits

Posted on April 5th, 2011 by Lu�s Cruz

- Fourier Transform study

- FFT and iFFT python tutorial study

- Frequency domain signals study

- Difficulties

- Frequency domain to impulse response conversion.

- Causality Enforcement on frequency domain signals

Posted on March 20th, 2011 by Lu�s Cruz

- Jitter software Documentation draft creation ends

- Updated jitter software tool to ensure coherence with documentation

- Difficulties

- It's being difficult to conciliate job and family time with thesis time

- PC issues (solved)

Posted on March 8th, 2011 by Lu�s Cruz

- Jitter software Documentation creation started

- Documentation figures creation

Posted on March 8th, 2011 by Lu�s Cruz

- Jitter software decomposition tool uploaded to

Resources page

- The jitter tool was developed using python

- Multi-thread was added to the tool, decreasing the overall processing time (on multi core CPUs)

- Difficulties

- The conversion from python to an executable windows file

(special python commands were needed to ensure correct support of multi-thread)

- The jitter histograms acquire on lab have a big time step resulting on a less accurate

jitter decomposition values

Posted on March 8th, 2011 by Lu�s Cruz

- Lab Reports analysis

- Silicon raw data was acquired to be used on the development process

- Jitter histograms were stored on .csv files

- One of the difficulties of using post processed data is

the lack of information about the signal behavior

- Jitter histograms have a bigger time step

Posted on February 20th, 2011 by Lu�s Cruz

- Meeting with the advisor

- MIPI, HDMI and USB standards study

- Specification of the principal measures done by the software tool

- Eye diagram generation

- Jitter decomposition

- Intra-Pair skew measurement

- Inter-Pair skew measurement

- Rise and Fall times measurement

- Minimum and Maximum values of the analog signal for each digital representation

- Draft specification of the software engine

19Fev (100%)

19Fev (100%)

26Fev (100%)

26Fev (100%)

10May (100%)

10May (100%)

31May (100%)

31May (100%)

23Jun (100%)

23Jun (100%)

26Jul (0%)

26Jul (0%)